This digital design project involved writing multiple Verilog modules to create the machine in the figure on an FPGA. Using the ‘Program Counter’ this machine could run through a series of instructions that were stored in the RAM.

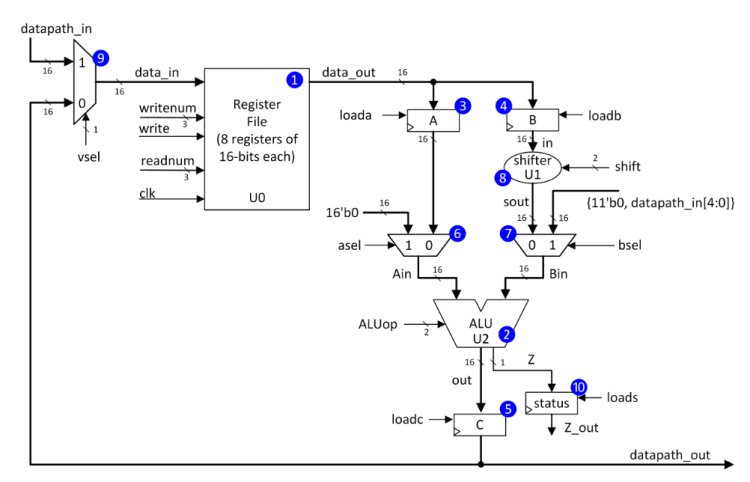

Datapath

This module allowed for registers to be added or subtracted, as well as multiplying or dividing by 2. The results could be sent to another module or stored back in the registers.

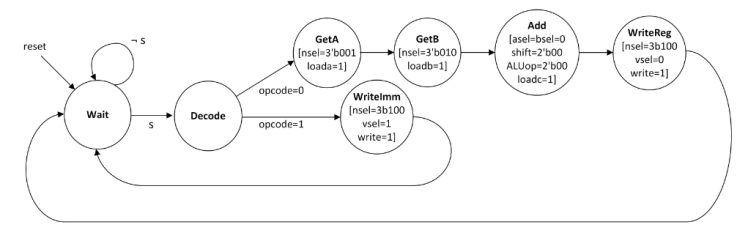

State Machine

This module allowed for a sequence of events to occur with a single inputted bus.